WHY THIS MATTERS IN BRIEF

Berkeley Lab breakthrough might help to reboot Moores Law.

Transistor size is an important part of improving the price-performance of today’s computer systems – the smaller your transistors, the more you can fit on a chip and the faster and more efficient your processor can be.

Accomplishing what was theorized to be impossible according to the laws of physics, UC Berkeley professor of electrical engineering and computer sciences Ali Javey and his research team have created the smallest transistor to date which could pave the way for faster electronics in the future.

Over the past few years Moores Law has been under pressure and up until now companies and academics alike have been trying to create ever smaller transistors by experimenting with new materials and platforms such as carbon nanotubes, molecular computing as well as light based computing systems but working from the US Department of Energy’s Lawrence Berkeley National Laboratory, faculty scientist Javey and his team have shown it is possible to create a functional 1-nanometer gate in a transistor if the correct material and proper design are implemented. A collaboration of teams from UC Berkeley, Stanford University and the University of Texas at Dallas published their findings last week in the journal Science.

“Basically the goal of the industry (is) every two years we try to reduce the transistor size,” said Sujay Desai, UC Berkeley graduate student and lead student on his research team.

“This is to improve the performance and the density of electronics on the same area of an electronic chip.”

According to Desai, transistors are used as the smallest component of every electric circuit and are essentially an “electric switch.” They are used in cell phones, computers, televisions and other electronics. The device contains three different terminals — a source, a drain and a gate. The electric current is controlled by the gate and flows between the source and the drain.

Currently, transistors on the market have gates that are typically 20 nanometers in size with new 10nm and 7nm chips due for release by Intel – with their Cannonlake product – and Global Foundries in 2017 and 2018 respectively. Previously, scientists predicted the gates could be no smaller than 5 nanometers because the small size of the gate would be unable to control the electric current flowing between the source and the drain — a quantum mechanical effect known as “Quantum Tunneling” where electrons can jump out of one channel into another making the chips useless.

The research team used a different material and a new architectural design to address the issue of tunneling, Desai said.

The semiconductor channel material through which the current flows is a crystal and in most transistors is silicon, which allows for a lower electron effective mass but is only functional in larger gate lengths. Electron effective mass is the amount of resistance an electron receives moving through a crystal.

“We decided to use MoS2 as the channel material instead,” Desai said.

“Because (MoS2) has a higher electron effective mass, you are able to reduce the tunneling in electrons even if it is a smaller gate length.”

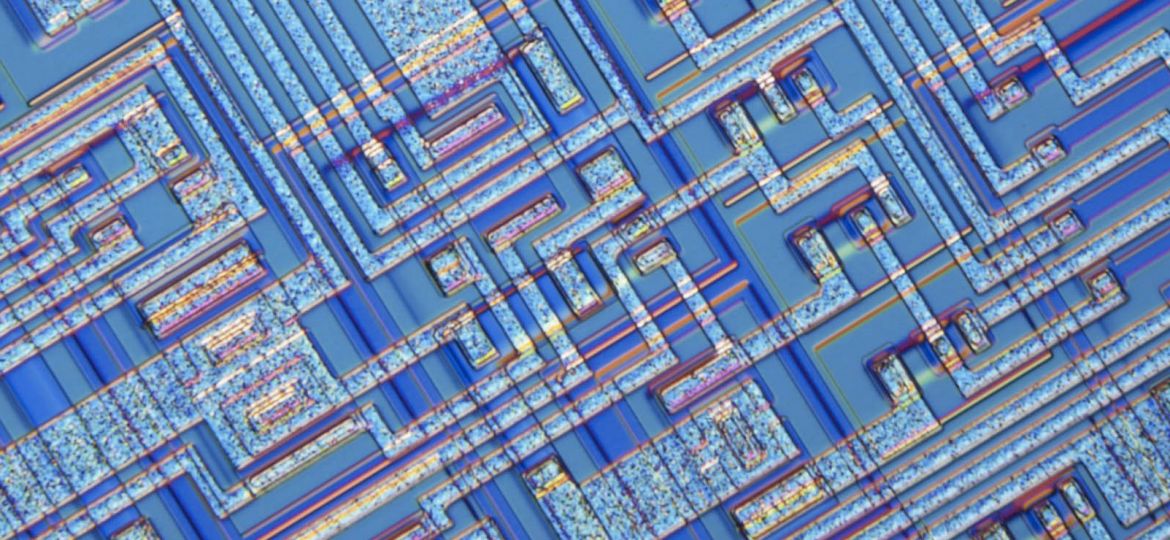

Schematic of the new transistor

Moon Kim, a professor at the University of Texas at Dallas said his team’s role was to design a physical structure that reduces the amount of energy lost when the current moves from the source to the drain.

Desai noted the design of the structure still needs to improve before the technology can become a reality.

“For me, it’s exciting because it shows that we can calculate the behaviour of electrons that are moving over very short distances,” said Marvin Cohen, a UC Berkeley professor of physics, “and for the technology industry, this will help to make their computers and cellphones and devices much more efficient.”